-

HBM (High Bandwidth Memory) 고밀도 메모리와 TSMC 동향반도체 이야기 2024. 3. 26. 00:56반응형

HBM(고밀도 메모리)은 High Bandwidth Memory의 약자로, 그래픽 처리 장치(GPU) 및 고성능 컴퓨팅 시스템과 같은 고성능 애플리케이션에서 사용되는 고성능 및 고밀도 메모리 기술입니다. HBM은 높은 대역폭과 낮은 전력 소비를 결합하여 최신 기술의 그래픽 카드 및 기타 애플리케이션에 필수적인 메모리 시스템으로 널리 사용됩니다.

HBM은 일반적으로 GPU 칩과 함께 패키징되며, 그래픽 카드 또는 시스템 보드의 상단에 탑재됩니다. 이 기술은 기존의 GDDR(그래픽 더블 데이터 속도) 메모리와 비교하여 더 높은 대역폭을 제공합니다. 대역폭은 데이터를 메모리에서 프로세서(예: GPU)로 더 빠르게 이동시킬 수 있는 능력을 의미합니다. 이로써 그래픽 처리나 병렬 컴퓨팅 작업 등에 필요한 데이터 처리량을 크게 향상시킬 수 있습니다.

HBM은 여러 개의 메모리 다이를 3차원적으로 적층하여 제조됩니다. 이러한 3D 적층 구조는 더 많은 메모리 용량을 더 작은 공간에 넣을 수 있도록 합니다. 또한, HBM은 전력 효율적이기 때문에 더 높은 성능을 위해 더 적은 전력을 소비합니다.

이러한 특성으로 인해 HBM은 고성능 컴퓨터 그래픽스, 인공 지능, 딥 러닝, 고성능 컴퓨팅 등의 분야에서 널리 사용되고 있습니다. 또한, 이 기술은 미래의 그래픽 처리 및 데이터 중심 애플리케이션에 대한 요구를 충족시키기 위해 지속적으로 발전하고 있습니다.

TSMC(Taiwan Semiconductor Manufacturing Company)는 세계적으로 유명한 반도체 생산 업체 중 하나로, 혁신적인 기술과 고성능 칩을 제조하는 데 특히 주력하고 있습니다. 여러 기술 중에서 TSMC가 최근에 개발하거나 도입한 몇 가지 기술을 살펴보겠습니다.

- 5나노미터 공정 기술: TSMC는 5나노미터 공정 기술을 개발하여 혁신적인 칩을 제조하고 있습니다. 이 기술은 칩의 소자들을 더 밀도 높게 배치하여 더 작고 더 효율적인 칩을 만드는 데 도움이 됩니다. 또한, 더 높은 성능과 더 낮은 전력 소비를 가능하게 합니다.

- 진화된 3D 적층 기술: TSMC는 3차원 적층 기술을 개선하여 더 높은 성능과 효율성을 달성하고 있습니다. 이 기술은 칩 내의 여러 층에 다양한 기능을 통합함으로써 공간을 절약하고 전력 소모를 최소화합니다.

- Extreme Ultraviolet Lithography (EUV): EUV 리소그래피는 더 작고 복잡한 패턴을 만드는 데 사용되는 혁신적인 노광 기술입니다. TSMC는 EUV 기술을 적용하여 더 높은 해상도와 정확도로 칩을 제조할 수 있습니다. 이는 더 높은 성능과 더 낮은 에너지 소비를 가능케 합니다.

- 통합 패키징 기술: TSMC는 다양한 칩과 다양한 기능을 단일 패키지에 통합하는 고급 패키징 기술을 개발하고 있습니다. 이는 칩간 통신 속도를 높이고 시스템의 효율성을 향상시키는 데 도움이 됩니다.

TSMC(Taiwan Semiconductor Manufacturing Company)는 세계적으로 유명한 반도체 제조 기업 중 하나로, 최첨단 기술과 혁신적인 제조 공정을 통해 다양한 제품을 제공하고 있습니다. TSMC의 신 기술 중 하나는 HBM(High Bandwidth Memory)과 관련된 것입니다.

TSMC는 HBM 기술을 제조 과정에 적용하여 고성능 및 고밀도 메모리 칩을 제조합니다. 이러한 칩은 그래픽 카드, 고성능 컴퓨팅 시스템 및 기타 특정 애플리케이션에 사용됩니다.

TSMC의 제조 과정은 HBM을 통합하여 2.5D 또는 3D 적층 패키징 기술을 사용합니다. 이것은 다수의 메모리 다이를 고성능 칩 위에 직접 적층하는 것을 의미합니다. 이러한 3D 적층 구조는 공간 효율성과 전력 효율성을 크게 향상시킵니다.

또한, TSMC는 HBM과 함께 사용되는 고급 시스템 인터커넥션 기술도 개발하고 있습니다. 이 기술은 메모리와 프로세서 간의 데이터 통신을 더욱 효율적으로 만들어 대역폭을 극대화합니다.

이렇게 함으로써 TSMC는 고성능 및 고대역폭 요구를 충족하는 혁신적인 반도체 솔루션을 제공하고 있으며, 이는 그래픽 처리, 인공 지능, 딥 러닝 및 고성능 컴퓨팅 분야에서 사용되고 있습니다. 이러한 기술의 발전은 새로운 시스템 및 응용 분야에서 더욱 빠르고 효율적인 데이터 처리를 가능하게 합니다.

TSMC의 패키징 기술은 다른 반도체 제조 업체와 어떻게 다를까요? 이 질문에 대답하려면 다른 패키징 기술과의 주요 차이점을 이해해야 합니다.

- 고급 패키징 기술의 보급화: TSMC는 최신 패키징 기술을 개발하고 보급화하는 데 큰 투자를 하고 있습니다. 이로 인해 TSMC의 고급 패키징 기술은 다른 업체보다 더 빠르게 채택되고 있습니다.

- 3D 적층 기술의 활용: TSMC는 3D 적층 기술을 활용하여 고성능 및 고밀도 패키지를 제공합니다. 이러한 기술은 공간 효율성과 전력 효율성을 크게 향상시킵니다.

- 고급 인터커넥션 기술: TSMC는 패키지 내에서 다양한 칩 간의 통신을 최적화하는 고급 인터커넥션 기술을 제공합니다. 이는 전력 소비를 줄이고 성능을 향상시킵니다.

- 고급 재료 및 공정 기술: TSMC는 고급 재료와 공정 기술을 사용하여 패키지 내부의 더 높은 신호 품질과 안정성을 제공합니다.

- 신속한 기술 혁신: TSMC는 기술 혁신에 대한 끊임없는 투자로 빠르게 변화하는 시장에 대응합니다. 이는 더 빠른 속도로 새로운 패키징 기술을 개발하고 도입할 수 있음을 의미합니다.

이러한 요소들로 인해 TSMC의 패키징 기술은 다른 업체와 비교했을 때 높은 수준의 성능, 효율성 및 혁신성을 보여주고 있습니다. 이는 TSMC가 현재 반도체 산업에서 주요한 역할을 하고 있음을 보여줍니다.

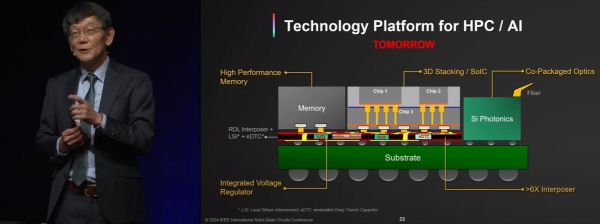

실리콘 포토닉스를 탑재한 신규 패키징 플랫폼_케빈 장 TSMC 수석 부사장 세계 최대 파운드리 기업인 TSMC가 실리콘 포토닉스를 활용한 차세대 고성능 컴퓨팅(HPC) 및 인공지능(AI)용 패키징 플랫폼을 공개했습니다. 실리콘 포토닉스는 광자를 활용한 반도체 기술로, 미래 반도체 기술의 중요한 부분으로 간주됩니다. TSMC의 실리콘 포토닉스 기술 도입은 인터커넥트를 개선하고 성능을 향상시키기 위한 시도로 해석됩니다.

TSMC의 수석 부사장인 케빈 장은 '국제 고체 회로학회(ISSCC) 2024'에서 실리콘 포토닉스를 활용한 패키징 플랫폼에 대해 발표했습니다. 그는 미래의 고성능 컴퓨팅 요구 사항을 충족시키기 위해서는 인공지능 가속기(AI 가속기)의 성능을 향상시켜야 한다고 강조했습니다. 이를 위해서는 반도체를 수직으로 쌓고 여러 최첨단 칩을 함께 사용해야 한다고 설명했습니다.

AI 가속기의 성능 향상을 위해서는 칩 렛(chiplet)과 고대역폭 메모리(HBM)를 탑재하는 비율을 늘려야 한다는 것을 지적했습니다. 칩 렛은 모놀리식(Monolithic) 구조가 아닌 여러 다이를 연결하여 하나의 칩처럼 동작하게 만드는 기술을 의미합니다. 이는 웨이퍼 수율을 개선하고 생산 비용을 절감하는데 도움이 됩니다.

이러한 기술을 확대하기 위해서는 인터포저(interposer) 및 칩 온 웨이퍼 온 서브스트레이트(CoWoS) 기술의 확대가 필요하다고 덧붙였습니다. 그는 TSMC가 실리콘 포토닉스 기술을 도입하여 이러한 과제에 대응한다고 설명했습니다. 실리콘 포토닉스는 기존의 입출력(I/O)보다 광 섬유를 통해 데이터 전송이 이뤄지기 때문에 입출력(I/O)가 개선될 것으로 기대됩니다.

또한, 장 부사장은 전력 공급 문제를 해결하기 위해 전압 조정기(IVR)를 탑재할 수 있다고 설명했습니다. IVR은 전력 회로를 통해 전력 소비를 줄일 수 있습니다.

마지막으로, 장 부사장은 현재의 최첨단 트랜지스터 기술을 사용하면 약 1000억 개의 트랜지스터를 하나의 다이에 집적할 수 있지만, 이것만으로는 미래의 AI 애플리케이션에 대응하기 어렵다고 강조했습니다. 그는 3D 패키징 기술을 활용하면 1조 개의 트랜지스터를 탑재할 수 있으며, 이것이 미래의 연산에 대응하는 방법이라고 덧붙였습니다.

반응형'반도체 이야기' 카테고리의 다른 글

왜 삼성은 반도체 기술력에서 TSMC에 뒤쳐지고 있는가? (2) 2024.03.26